成功率和可靠性驅(qū)動的納米尺度集成電路設(shè)計方法學(xué)

隨著半導(dǎo)體工藝節(jié)點持續(xù)向納米尺度演進(jìn),集成電路設(shè)計面臨著前所未有的挑戰(zhàn)。傳統(tǒng)的、以性能和面積為單一核心導(dǎo)向的設(shè)計范式,在深亞微米及以下節(jié)點已顯得捉襟見肘。工藝偏差、量子隧穿效應(yīng)、電源電壓波動、熱效應(yīng)以及日益加劇的軟錯誤率等問題,嚴(yán)重威脅著芯片的功能正確性、性能穩(wěn)定性和長期可靠性。因此,一種以“成功率和可靠性”為雙重核心驅(qū)動力的新型設(shè)計方法學(xué)應(yīng)運而生,成為納米尺度集成電路設(shè)計的必然選擇。

一、 核心挑戰(zhàn):從確定性到概率性設(shè)計的轉(zhuǎn)變

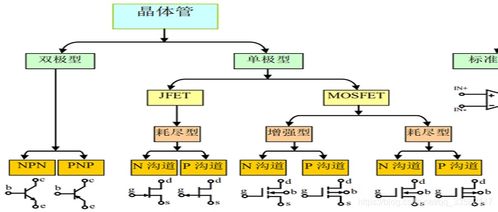

在成熟工藝節(jié)點,設(shè)計參數(shù)(如延遲、功耗)通常被認(rèn)為在可控范圍內(nèi)呈確定性分布。進(jìn)入納米尺度后,原子級的工藝波動(如柵氧厚度、摻雜濃度、線寬邊緣粗糙度)導(dǎo)致晶體管和互連的特性呈現(xiàn)顯著的空間(同一芯片不同位置)和時間(同一晶體管不同時間)隨機(jī)性。這使得芯片的性能、功耗乃至功能都變得具有概率性特征。設(shè)計目標(biāo)不再是追求一個絕對的最優(yōu)值,而是在給定的工藝擾動下,最大化芯片能夠滿足所有規(guī)格(功能、時序、功耗)的概率,即“首次硅成功率”(First Silicon Success Rate)和整個生命周期內(nèi)的“可靠性”(Reliability)。

二、 方法學(xué)支柱:預(yù)測、建模與協(xié)同優(yōu)化

成功率和可靠性驅(qū)動的方法學(xué)建立在三大支柱之上:

- 精準(zhǔn)的統(tǒng)計建模與仿真:這是方法學(xué)的基石。需要建立能夠精確刻畫工藝波動、電壓噪聲、溫度變化以及老化效應(yīng)(如偏置溫度不穩(wěn)定性BTI、熱載流子注入HCI)的統(tǒng)計模型。這些模型被集成到設(shè)計流程的各個階段,從電路級仿真(如蒙特卡洛分析)到靜態(tài)時序分析(采用統(tǒng)計靜態(tài)時序分析SSTA),再到物理設(shè)計,確保設(shè)計決策基于對變異性的全面評估。

- 設(shè)計階段的可靠性內(nèi)建(Design-for-Reliability, DfR):將可靠性考量從“事后補(bǔ)救”前置到“主動設(shè)計”。這包括:

- 抗變異設(shè)計:采用電路技術(shù)(如使用反饋結(jié)構(gòu)、提高器件尺寸以降低相對波動影響)、版圖技術(shù)(如共同質(zhì)心布局、添加冗余通孔)來抑制工藝波動的影響。

- 容錯設(shè)計:對于無法完全消除的軟錯誤(如宇宙射線引起的單粒子翻轉(zhuǎn)),在關(guān)鍵路徑和存儲單元引入糾錯碼(ECC)、三模冗余(TMR)或自定時電路等容錯機(jī)制。

- 老化感知設(shè)計:在設(shè)計階段預(yù)測電路在生命周期內(nèi)的性能退化,并通過留出時序裕量(老化防護(hù)帶)、采用老化不敏感的電路結(jié)構(gòu)或動態(tài)電壓頻率調(diào)節(jié)(DVFS)來補(bǔ)償。

- 跨層次、跨領(lǐng)域的協(xié)同分析與優(yōu)化:打破傳統(tǒng)設(shè)計流程中前端(邏輯設(shè)計)與后端(物理設(shè)計)、數(shù)字與模擬、芯片與封裝/系統(tǒng)的壁壘。實現(xiàn)從系統(tǒng)架構(gòu)、微結(jié)構(gòu)、邏輯設(shè)計、物理實現(xiàn)到制造測試的垂直整合與迭代優(yōu)化。例如,系統(tǒng)架構(gòu)可以選擇冗余線程或可降級模式來容忍底層硬件的偶發(fā)錯誤;物理設(shè)計工具需要以統(tǒng)計良率和可靠性為優(yōu)化目標(biāo),而不僅僅是線長和時序。

三、 關(guān)鍵技術(shù)與工具演進(jìn)

機(jī)器學(xué)習(xí)輔助的建模與優(yōu)化:利用機(jī)器學(xué)習(xí)技術(shù)從海量制造和測試數(shù)據(jù)中學(xué)習(xí)并預(yù)測工藝-設(shè)計-可靠性之間的復(fù)雜非線性關(guān)系,加速統(tǒng)計模型的構(gòu)建,并智能探索設(shè)計空間,找到高魯棒性的設(shè)計方案。

硅后調(diào)諧與自適應(yīng)系統(tǒng):承認(rèn)納米尺度下完全依靠設(shè)計前預(yù)測的局限性,在芯片中嵌入傳感器(監(jiān)測溫度、電壓、延遲等)和調(diào)節(jié)機(jī)制(如可調(diào)體偏置、自適應(yīng)時鐘分配)。芯片能夠在運行時根據(jù)實際工作條件和老化狀態(tài)進(jìn)行動態(tài)調(diào)整,始終將性能與可靠性維持在最優(yōu)區(qū)間。

* 電子設(shè)計自動化(EDA)工具的革命:EDA工具鏈需要全面升級,支持從RTL到GDSII的全流程統(tǒng)計分析與優(yōu)化。工具需要具備處理大規(guī)模統(tǒng)計模型的能力,并提供以良率和可靠性為度量的設(shè)計收斂指導(dǎo)。

四、 結(jié)論與展望

成功率和可靠性驅(qū)動的設(shè)計方法學(xué),標(biāo)志著集成電路設(shè)計從追求“理想性能”向保障“實際可用”的深刻轉(zhuǎn)變。它不再將工藝波動和可靠性衰減視為需要克服的“敵人”,而是作為設(shè)計必須理解和駕馭的“內(nèi)在屬性”。隨著工藝向3nm及以下節(jié)點、三維集成和新興器件(如碳納米管、二維材料)發(fā)展,變異性和可靠性挑戰(zhàn)將更加嚴(yán)峻。這一方法學(xué)將與異構(gòu)集成、存算一體、近似計算等新興架構(gòu)深度融合,通過更智能、更自適應(yīng)、更協(xié)同的設(shè)計手段,為后摩爾時代持續(xù)釋放集成電路的性能潛力,并確保其在從消費電子到自動駕駛、航空航天等關(guān)鍵任務(wù)應(yīng)用中穩(wěn)定可靠地運行。這不僅是技術(shù)路徑的演進(jìn),更是設(shè)計哲學(xué)的一次重要革新。

如若轉(zhuǎn)載,請注明出處:http://m.chao321.cn/product/62.html

更新時間:2026-01-07 05:11:05