CMOS開關(guān)電路設(shè)計(jì) 從理論到實(shí)踐的論壇交流熱點(diǎn)

在當(dāng)今快速發(fā)展的半導(dǎo)體行業(yè)中,CMOS開關(guān)電路設(shè)計(jì)作為連接數(shù)字與模擬領(lǐng)域的關(guān)鍵技術(shù),一直是電子工程師和IC設(shè)計(jì)者關(guān)注的焦點(diǎn)。無論是專注于高性能模擬開關(guān)、低功耗數(shù)字切換,還是混合信號(hào)系統(tǒng)的集成,相關(guān)設(shè)計(jì)挑戰(zhàn)與解決方案的討論在各大專業(yè)論壇中始終保持著極高的熱度。

以EETOP、創(chuàng)芯網(wǎng)等為代表的集成電路設(shè)計(jì)論壇,已成為全球及中國半導(dǎo)體從業(yè)者不可或缺的知識(shí)分享與問題解答平臺(tái)。在這些論壇的“模擬電路設(shè)計(jì)”、“數(shù)字電路設(shè)計(jì)”或“混合信號(hào)設(shè)計(jì)”板塊中,CMOS開關(guān)電路的相關(guān)帖子層出不窮。討論內(nèi)容廣泛而深入,涵蓋基礎(chǔ)理論與高級(jí)應(yīng)用。

一、 核心設(shè)計(jì)挑戰(zhàn)與論壇熱議話題

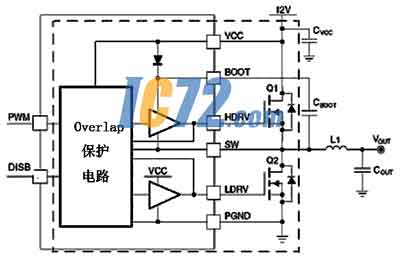

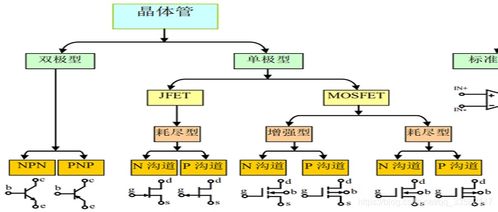

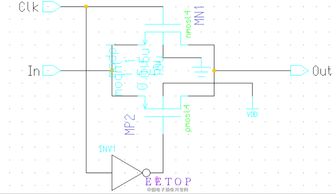

- 導(dǎo)通電阻(Ron)與線性度:這是模擬開關(guān)設(shè)計(jì)的核心。論壇中常探討如何通過晶體管尺寸、布局優(yōu)化以及創(chuàng)新架構(gòu)(如傳輸門結(jié)構(gòu))來降低Ron并改善其隨輸入電壓的變化,以滿足精密信號(hào)路徑的要求。

- 電荷注入與時(shí)鐘饋通:這些非理想效應(yīng)會(huì)引入誤差,尤其在采樣保持電路和精密數(shù)據(jù)采集系統(tǒng)中。資深工程師們經(jīng)常分享SPICE仿真技巧、版圖匹配技術(shù)以及電路補(bǔ)償方法,以最小化這些效應(yīng)的影響。

- 速度與帶寬:對(duì)于高頻應(yīng)用,開關(guān)的切換速度和關(guān)斷隔離度是關(guān)鍵。論壇帖子會(huì)深入分析寄生電容的影響、驅(qū)動(dòng)電路的設(shè)計(jì),以及深亞微米工藝下如何權(quán)衡速度、功耗與面積。

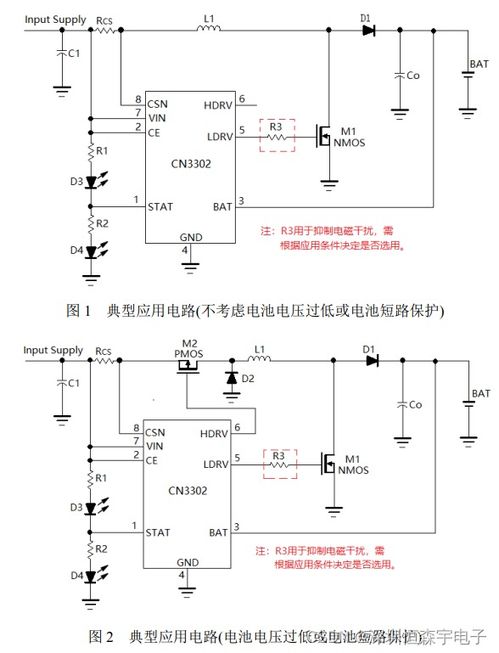

- 功耗與電源管理:在嵌入式設(shè)計(jì)和移動(dòng)設(shè)備中,低功耗至關(guān)重要。關(guān)于采用低電壓設(shè)計(jì)、電源域隔離和關(guān)斷技術(shù)的討論非常活躍。

- ESD與可靠性:作為芯片的“門戶”,開關(guān)電路的ESD保護(hù)設(shè)計(jì)是量產(chǎn)可靠性的保證。論壇中常有關(guān)于各種ESD結(jié)構(gòu)(如GGNMOS、RC-Clamp)在開關(guān)電路集成中利弊的實(shí)踐經(jīng)驗(yàn)交流。

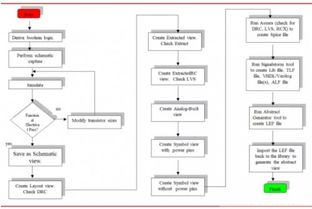

二、 設(shè)計(jì)流程與工具交流

論壇不僅是問題解答的場所,也是設(shè)計(jì)方法論交流的平臺(tái)。從行為級(jí)建模(Verilog-A/AMS)、電路級(jí)仿真(SPICE)、到物理版圖設(shè)計(jì),每個(gè)階段都有大量經(jīng)驗(yàn)分享。成員們會(huì)討論如何設(shè)置合理的仿真邊界條件,解讀工藝設(shè)計(jì)套件(PDK)中的復(fù)雜模型,以及進(jìn)行后仿真的注意事項(xiàng)。版圖設(shè)計(jì)中的匹配性、隔離、閂鎖效應(yīng)預(yù)防等實(shí)踐性極強(qiáng)的內(nèi)容,更是圖文并茂的熱點(diǎn)。

三、 跨領(lǐng)域融合與趨勢展望

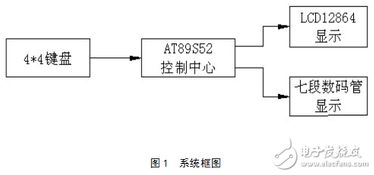

在“集成電路設(shè)計(jì)”和“嵌入式設(shè)計(jì)”的交叉領(lǐng)域,CMOS開關(guān)的角色愈發(fā)重要。例如,在微控制器(MCU)的模擬前端(AFE)、可編程增益放大器(PGA)中,開關(guān)是構(gòu)成配置網(wǎng)絡(luò)的基礎(chǔ)。論壇討論也緊跟行業(yè)趨勢,涉及先進(jìn)工藝節(jié)點(diǎn)(如FinFET)下開關(guān)設(shè)計(jì)的新特性、用于射頻(RF)領(lǐng)域的CMOS開關(guān)設(shè)計(jì),以及面向物聯(lián)網(wǎng)(IoT)傳感器的超低泄漏開關(guān)方案。

EETOP、創(chuàng)芯網(wǎng)等電子工程師論壇構(gòu)建了一個(gè)充滿活力的技術(shù)生態(tài)系統(tǒng)。無論是初入行的新手尋找學(xué)習(xí)路徑,還是資深專家探討前沿難題,關(guān)于CMOS開關(guān)電路設(shè)計(jì)的交流都在持續(xù)推動(dòng)著技術(shù)的進(jìn)步與實(shí)踐經(jīng)驗(yàn)的沉淀。這些討論不僅解決了具體的設(shè)計(jì)問題,更在無形中塑造著中國乃至全球半導(dǎo)體設(shè)計(jì)社區(qū)的集體智慧與創(chuàng)新能力。對(duì)于每一位投身于電子電路、半導(dǎo)體與集成電路設(shè)計(jì)的技術(shù)人員而言,積極參與這些論壇的討論,無疑是保持技術(shù)敏感度、突破設(shè)計(jì)瓶頸的寶貴途徑。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.chao321.cn/product/56.html

更新時(shí)間:2026-01-07 07:36:37