驅(qū)動反相器在模擬射頻集成電路設計中的關(guān)鍵作用

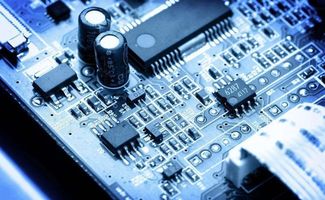

在半導體集成電路(IC)設計的廣闊領(lǐng)域中,模擬射頻(Analog RF)IC設計占據(jù)著核心地位,尤其在無線通信、物聯(lián)網(wǎng)和嵌入式系統(tǒng)等應用中。驅(qū)動反相器作為模擬RF IC設計的關(guān)鍵組件,其性能直接影響系統(tǒng)的整體效率、功耗和信號完整性。本文將圍繞驅(qū)動反相器的設計原則、在模擬RF IC中的應用挑戰(zhàn)以及行業(yè)趨勢展開討論。

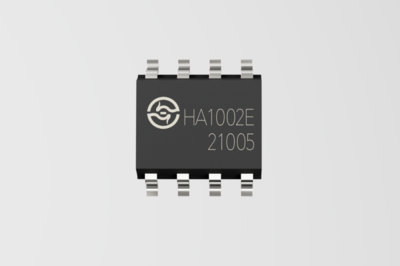

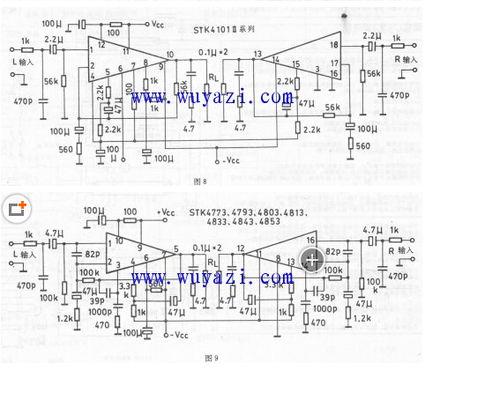

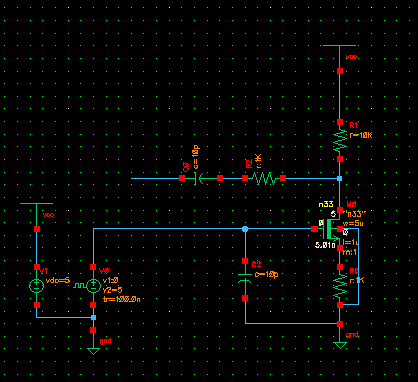

驅(qū)動反相器是一種常見的邏輯和模擬電路元件,用于信號的反相和驅(qū)動。在模擬RF IC中,它通常用于功率放大器(PA)、混頻器和振蕩器等模塊,以提供足夠的增益和輸出驅(qū)動能力。設計驅(qū)動反相器時,工程師需關(guān)注多個關(guān)鍵參數(shù),如轉(zhuǎn)換速率、輸出阻抗、噪聲性能和功耗。例如,在高頻RF應用中,反相器的開關(guān)速度和線性度至關(guān)重要,以避免信號失真和效率下降。工藝節(jié)點選擇(如CMOS或GaAs)也會影響設計,需在成本和性能間取得平衡。

模擬RF IC設計面臨諸多挑戰(zhàn),包括熱管理、寄生效應和電磁干擾(EMI)。驅(qū)動反相器在這些挑戰(zhàn)中扮演重要角色。例如,在嵌入式系統(tǒng)中,功耗優(yōu)化是關(guān)鍵,驅(qū)動反相器的設計需采用低功耗技術(shù),如亞閾值操作或多閾值器件。EETOP等專業(yè)論壇作為最大最火的半導體集成電路社區(qū),為工程師提供了寶貴的交流平臺,分享實際案例和仿真工具(如Cadence或ADS)的使用經(jīng)驗,幫助解決設計難題。

集成電路設計的發(fā)展趨勢正推動驅(qū)動反相器的創(chuàng)新。隨著5G和6G技術(shù)的普及,對高頻、高線性度的RF IC需求激增。驅(qū)動反相器需集成更多智能功能,如自適應偏置和數(shù)字輔助校準,以提升系統(tǒng)可靠性。電子電路和嵌入式設計的融合也促使設計者采用混合信號方法,將模擬RF IC與數(shù)字處理單元緊密結(jié)合。

驅(qū)動反相器在模擬RF IC設計中不可或缺,其優(yōu)化直接關(guān)系到整體電路的性能。借助EETop等社區(qū)的資源和行業(yè)合作,工程師能更高效地應對復雜設計任務,推動半導體技術(shù)的進步。隨著AI和物聯(lián)網(wǎng)的擴展,驅(qū)動反相器的設計將繼續(xù)演進,為更小、更快、更節(jié)能的IC解決方案鋪平道路。

如若轉(zhuǎn)載,請注明出處:http://m.chao321.cn/product/41.html

更新時間:2026-01-07 05:30:51