模擬集成電路設(shè)計(jì)原理習(xí)題解析

模擬集成電路(Analog Integrated Circuits,簡(jiǎn)稱(chēng)模擬IC)設(shè)計(jì)是電子工程領(lǐng)域的核心課程之一,其設(shè)計(jì)原理涉及半導(dǎo)體物理、電路理論、信號(hào)處理和工藝技術(shù)等多學(xué)科知識(shí)。本文針對(duì)模擬集成電路設(shè)計(jì)中的典型習(xí)題進(jìn)行講解,幫助讀者深入理解關(guān)鍵概念和設(shè)計(jì)方法。

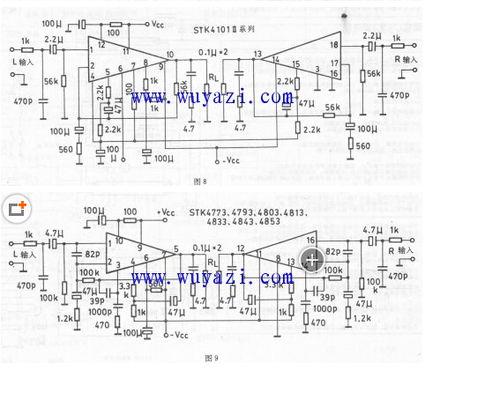

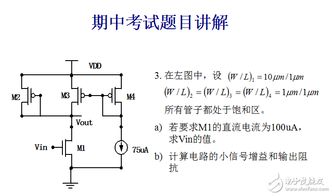

一、差分放大器設(shè)計(jì)習(xí)題

問(wèn)題:設(shè)計(jì)一個(gè)差分放大器,要求差模增益為100,共模抑制比(CMRR)大于80dB,電源電壓為±5V。請(qǐng)確定晶體管尺寸和偏置電路。

解析:差分放大器是模擬IC中的基本模塊。差模增益Ad≈gm*Rc,其中g(shù)m為跨導(dǎo),Rc為負(fù)載電阻。設(shè)Ad=100,可推導(dǎo)出gm與Rc的關(guān)系。CMRR取決于電流源的輸出阻抗和晶體管匹配性。為實(shí)現(xiàn)CMRR>80dB,需采用高輸出阻抗的電流源(如共源共柵結(jié)構(gòu))并確保晶體管尺寸匹配。根據(jù)電源電壓±5V,偏置電路應(yīng)設(shè)置靜態(tài)工作點(diǎn),使晶體管處于飽和區(qū)。例如,使用電流鏡提供尾電流,并計(jì)算W/L比以滿(mǎn)足gm需求。建議仿真驗(yàn)證直流工作點(diǎn)和交流性能。

二、運(yùn)算放大器穩(wěn)定性分析習(xí)題

問(wèn)題:一個(gè)兩級(jí)運(yùn)算放大器在閉環(huán)增益為10時(shí)出現(xiàn)振蕩,如何通過(guò)補(bǔ)償電容改善穩(wěn)定性?

解析:振蕩通常由相位裕度不足引起。兩級(jí)運(yùn)放的主極點(diǎn)位于第一級(jí)輸出,次極點(diǎn)在第二級(jí)輸出。補(bǔ)償電容Cc可引入一個(gè)左半平面零點(diǎn)并降低次極點(diǎn)頻率,從而提高相位裕度。根據(jù)米勒效應(yīng),將Cc連接在第二級(jí)輸入和輸出之間,等效電容增大約為AvCc(Av為第二級(jí)增益)。通過(guò)計(jì)算開(kāi)環(huán)傳遞函數(shù),調(diào)整Cc值使相位裕度大于45°。習(xí)題中可假設(shè)第一級(jí)跨導(dǎo)gm1=1mA/V,第二級(jí)gm2=2mA/V,負(fù)載電容CL=5pF,計(jì)算Cc的近似值(例如Cc≈2.2CL/gm2*R1,其中R1為第一級(jí)輸出電阻)。用波特圖驗(yàn)證補(bǔ)償效果。

三、帶隙基準(zhǔn)源設(shè)計(jì)習(xí)題

問(wèn)題:設(shè)計(jì)一個(gè)帶隙基準(zhǔn)電路,輸出1.2V電壓,溫度系數(shù)低于20ppm/°C。說(shuō)明原理并計(jì)算電阻比例。

解析:帶隙基準(zhǔn)利用雙極性晶體管的VBE負(fù)溫度系數(shù)和ΔVBE正溫度系數(shù)相互補(bǔ)償。輸出Vref=VBE+KΔVBE,其中K為電阻比例因子。標(biāo)準(zhǔn)帶隙電壓約1.2V,對(duì)應(yīng)硅的帶隙電壓。設(shè)VBE=0.7V(在27°C),ΔVBE=VTln(N),VT為熱電壓,N為發(fā)射區(qū)面積比。通過(guò)調(diào)整電阻比R2/R1,使K*ΔVBE補(bǔ)償VBE的變化。溫度系數(shù)計(jì)算需對(duì)Vref求導(dǎo),令其接近零。例如,假設(shè)N=8,VT=26mV,則ΔVBE≈54mV,解得K≈9.3(即R2/R1比例)。實(shí)際設(shè)計(jì)中需考慮工藝偏差,建議用仿真優(yōu)化電阻值。

模擬集成電路設(shè)計(jì)習(xí)題需結(jié)合理論分析和實(shí)踐考慮。通過(guò)以上例題,讀者應(yīng)掌握差分放大器的增益與CMRR優(yōu)化、運(yùn)放的頻率補(bǔ)償方法以及帶隙基準(zhǔn)的溫度補(bǔ)償原理。多做習(xí)題并借助仿真工具(如SPICE)可深化理解,為實(shí)際芯片設(shè)計(jì)打下基礎(chǔ)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.chao321.cn/product/38.html

更新時(shí)間:2026-01-07 01:47:45